# intersil

### **Application Note 1647**

Author: David Sorlien

## ISL9112IRTNEVAL1Z, ISL9112IRT7EVAL1Z Evaluation **Board User Guide**

### **Evaluation Board Features**

- ISL9112IRTNZ high efficiency buck-boost regulator with I<sup>2</sup>C adjustable output voltage

- Input voltage rating from 1.8V to 5.5V

- I<sup>2</sup>C programmable output voltage, default 3.3V

- I<sup>2</sup>C programmable slew rate control

- 1200mA output current at  $V_{IN} \ge 3V$  and  $V_{OUT} = 3.3V$

- · 2.5MHz switching frequency

- Jumper selectable EN (enabled/disabled)

- Jumper selectable MODE (auto-PFM/forced-PWM)

- · Connectors, test points and jumpers for easy evaluation

## **Required Equipment**

- ISLUSBI2CKIT1Z (includes USB to I<sup>2</sup>C interface, USB cable and 4-pin  $I^2C$  cable)

- Power supply capable of delivering up to 5.5V and 3A

- Electronic load

- · Multimeter to measure voltages and currents

- Oscilloscope

### **Test Points, Connectors and** Jumpers

### TABLE 1. DESCRIPTION OF TEST POINTS

| TEST POINT(S) DESCRIPTION |                                                                                                                               |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| TP1                       | VOUT Kelvin connection for efficiency<br>measurements                                                                         |  |  |

| TP2                       | LX1 (Input side of power inductor)                                                                                            |  |  |

| TP3                       | PGND (Power ground)                                                                                                           |  |  |

| TP4                       | LX2 (Output side of power inductor)                                                                                           |  |  |

| TP5                       | PVIN Kelvin connection for efficiency<br>measurements                                                                         |  |  |

| TP6                       | VIN (supply input for internal reference)                                                                                     |  |  |

| TP7                       | SCL (I <sup>2</sup> C clock)                                                                                                  |  |  |

| TP8                       | SDA (I <sup>2</sup> C data)                                                                                                   |  |  |

| TP9                       | EN (Enable input, drive high to enable device)                                                                                |  |  |

| TP10                      | MODE/SYNC (Mode input, drive low for forced<br>PWM, or apply external clock between 2.75MHz<br>and 3.25MHz for external sync) |  |  |

| TP11, TP13, TP14          | GND (Ground)                                                                                                                  |  |  |

| TP12                      | FB (Voltage feedback input, connected to VOUT)                                                                                |  |  |

### **TABLE 2. DESCRIPTION OF CONNECTORS**

| CONNECTOR | DESCRIPTION                                      |  |  |

|-----------|--------------------------------------------------|--|--|

| J1        | Header for connecting input power                |  |  |

| J2        | Header for connecting external load              |  |  |

| J5        | Header for connecting I <sup>2</sup> C interface |  |  |

### TABLE 3. DESCRIPTION OF JUMPERS

| JUMPER | DESCRIPTION                                                                                                                                                                     |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J3     | Jumper to select EN input logic state. Set EN = VIN to<br>enable device, or set EN = GND to disable device.                                                                     |

| J4     | Jumper to select MODE input logic state. Set<br>MODE = VIN to enable auto-PFM mode, or set<br>MODE = GND to select forced PWM mode.                                             |

|        | To use external sync feature, remove this jumper and<br>apply an external clock between 2.75MHz and<br>3.25MHz on the MODE test point (TP10) or center pin<br>on the J4 header. |

### **Quick Setup Guide**

- 1. Install jumper on J3, shorting EN to VIN.

- 2. Install jumper on J4, shorting MODE to VIN.

- 3. Connect power supply to J1, with voltage setting between 1.8V and 5.5V.

- 4. Connect electronic load to J2.

- 5. Place scope probes on VOUT test point, and other test points of interest.

- 6. Turn on the power supply.

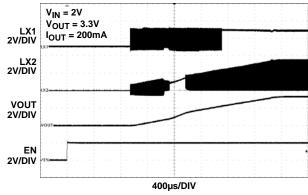

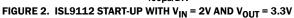

- 7. Monitor the output voltage start-up sequence on the scope. The waveforms will look similar to those shown in Figure 2 and Figure 3.

- 8. Turn on the electronic load.

- 9. Measure the output voltage with the voltmeter. The voltage should regulate within data sheet spec limits (FN7649).

- 10. To determine efficiency, measure input and output voltages at the Kelvin testpoints TP5 and TP1, and measure the input and output currents. Calculate efficiency based on these measurements.

- 11. To test external sync, remove the jumper at J4, then apply an external clock between 2.75MHz and 3.25MHz on the MODE input (test point TP10, or the center pin of header J4).

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. Copyright Intersil Americas Inc. 2011, 2012. All Rights Reserved.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

## Evaluation Software Installation/Use

- 1. Check your system specs against the system requirements listed below.

- Windows 98SE, Windows XP, or Windows NT

- CD-ROM drive

- USB port

- At least 20MB free hard disk space

- 1024x768 or larger resolution monitor

- 2. Install the driver for the ISLUSB2I2C interface by double clicking on the file named "ISLUSBI2C\_Driver\_Installer.exe" on the ISL9112 evaluation kit CD-ROM. Follow the instructions that appear on-screen to install the driver.

- 3. Install the ISL9112 evaluation software by double clicking on the file named: "ISL9112\_Eval\_Installer.exe" on the ISL9112 eval kit CD-ROM. Follow the instructions that appear on-screen to install the application.

- 4. Attach the ISLUSBI2C interface to the computer using the supplied USB cable. The 'Found New Hardware' dialog will appear. Select "Install the software automatically" and click "Next".

- 5. Locate the 4-wire I<sup>2</sup>C cable that is provided with the ISLUSBI2C kit. Attach one end of this cable to the 4-pin header on the ISLUSBI2C interface, and connect the other end of this cable to the corresponding 4-pin header on the ISL9112 evaluation board.

- 6. Following the "Quick Setup Guide" on page 1 of this document, connect the power supply, DC load, and other test equipment to the ISL9112 evaluation board, then apply power.

- 7. Launch the ISL9112 evaluation software. The installer adds a shortcut in the Start menu: Start  $\rightarrow$  Programs  $\rightarrow$  Intersil  $\rightarrow$  ISI9112  $\rightarrow$  ISL9112 Eval. Select this item to launch the evaluation software.

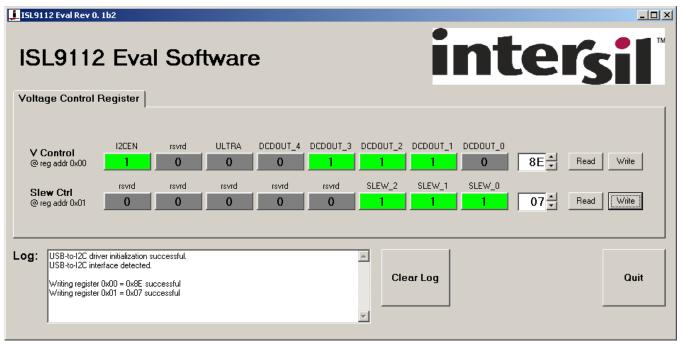

- 8. When launched, the ISL9112 evaluation software detects the ISLUSBI2C interface. At the bottom of the ISL9112 application window is a Log textbox. The message in this textbox should report: "USB-to-I2C driver initialization successful" and "USB-to-I2C interface detected." See Figure 1. If this message is not displayed, please check connections and try reinstalling the ISLUSBI2C driver.

- 9. Try reading the ISL9112 device registers by clicking on the READ buttons. Observe the activity reported in the Log textbox. Successful I<sup>2</sup>C communication will be reported in this textbox. If there is a communication error, this will also be reported in the Log textbox.

- 10. To change the output voltage, use Table 5 to determine the DCDOUT value that corresponds to the desired output voltage. Change the value of V Control register accordingly, and also set the I2CEN bit. Click the Write button to write this value to the device.

- **11.** To invoke Ultrasonic mode, set the ULTRA bit in the V Control register, and click the Write button to write this value to the device.

- 12. To change the slew rate setting, use Table 5 to determine the SLEWRATE value that corresponds to the desired slew rate. Change the value of the Slew Ctrl register accordingly, then click the Write button to write this data to the device under test.

- 13. To observe slew rate control behavior, set the slew rate to a value other than '0b000', and then change the DCDOUT value using the evaluation software. Observe  $V_{OUT}$  on an oscilloscope to see the slew rate limited transitions from one voltage setting to the new voltage setting.

FIGURE 1. ISL9112 EVALUATION SOFTWARE WINDOW

### **Typical Start-up Waveforms**

### **Slew Rate Control**

### TABLE 4. ISL9112 SLEW RATE CONTROL SETTINGS

| BIT | NAME     | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |

|-----|----------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0 | SLEWRATE | R/W  | 000   | Slew rate control (typ),<br>expressed as $\mu$ s per LSB<br>change in DCDOUT value:<br>0b000 = 0 $\mu$ s/ $\Delta$ LSB<br>0b001 = 1.5 $\mu$ s/ $\Delta$ LSB<br>0b010 = 3.1 $\mu$ s/ $\Delta$ LSB<br>0b100 = 12.5 $\mu$ s/ $\Delta$ LSB<br>0b101 = 25 $\mu$ s/ $\Delta$ LSB<br>0b101 = 25 $\mu$ s/ $\Delta$ LSB<br>0b110 = 50 $\mu$ s/ $\Delta$ LSB |

| 7:3 | Reserved | R/W  | 00000 |                                                                                                                                                                                                                                                                                                                                                    |

| TABLE 5. ISL9112 OUTPUT VOLTAGE SETTINGS |     |  |  |

|------------------------------------------|-----|--|--|

| DCDOUT[4:0]                              |     |  |  |

| 01.00000                                 | (V) |  |  |

| 060000                                   | 1.9 |  |  |

| 0b00001                                  | 2.0 |  |  |

| 0b00010                                  | 2.1 |  |  |

| 0b00011                                  | 2.2 |  |  |

| 0b00100                                  | 2.3 |  |  |

| 0b00101                                  | 2.4 |  |  |

| 0b00110                                  | 2.5 |  |  |

| 0b00111                                  | 2.6 |  |  |

| 0b01000                                  | 2.7 |  |  |

| 0b01001                                  | 2.8 |  |  |

| 0b01010                                  | 2.9 |  |  |

| 0b01011                                  | 3.0 |  |  |

| 0b01100                                  | 3.1 |  |  |

| 0b01101                                  | 3.2 |  |  |

| 0b01110                                  | 3.3 |  |  |

| 0b01111                                  | 3.4 |  |  |

| 0b10000                                  | 3.5 |  |  |

| 0b10001                                  | 3.6 |  |  |

| 0b10010                                  | 3.7 |  |  |

| 0b10011                                  | 3.8 |  |  |

| 0b10100                                  | 3.9 |  |  |

| 0b10101                                  | 4.0 |  |  |

| 0b10110                                  | 4.1 |  |  |

| 0b10111                                  | 4.2 |  |  |

| 0b11000                                  | 4.3 |  |  |

| 0b11001                                  | 4.4 |  |  |

| 0b11010                                  | 4.5 |  |  |

| 0b11011                                  | 4.6 |  |  |

| 0b11100                                  | 4.7 |  |  |

| 0b11101                                  | 4.8 |  |  |

| 0b11110                                  | 4.9 |  |  |

| 0b11111                                  | 5.0 |  |  |

|                                          |     |  |  |

## **Output Voltage Programming**

### TABLE 5. ISL9112 OUTPUT VOLTAGE SETTINGS

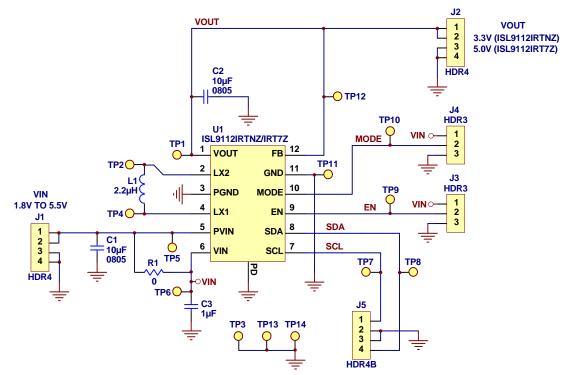

### **Evaluation Board Schematic**

FIGURE 4. ISL9112 EVALUATION BOARD SCHEMATIC

| ITEM# | QTY | DESIGNATORS                                                                        | PART TYPE                          | FOOTPRINT        | DESCRIPTION                                                                              | VENDORS     |

|-------|-----|------------------------------------------------------------------------------------|------------------------------------|------------------|------------------------------------------------------------------------------------------|-------------|

| 1     | 1   | U1                                                                                 | ISL9110IRTNZ<br>or<br>ISL9112IRT7Z | L12.3x3C<br>TQFN | Intersil ISL9112 Buck-Boost Regulator with I <sup>2</sup> C<br>Adjustable Output Voltage | INTERSIL    |

| 2     | 1   | L1                                                                                 | 2.2µH                              | 5x5x1.4          | NRS5020T2R2                                                                              | TAIYO YUDEN |

| 3     | 2   | C1, C2                                                                             | 10µF/10V/X5R                       | 0805             | LMK212BJ106KG                                                                            | TAIYO YUDEN |

| 4     | 1   | С3                                                                                 | 1µF/10V/X7R                        | 0603             | LMK107BJ105KK                                                                            | TAIYO YUDEN |

| 6     | 1   | R1                                                                                 | 0Ω                                 | 0603             | Resistor, Generic                                                                        | ANY         |

| 7     | 2   | J1, J2                                                                             | HDR-4                              | HDR-4            | Vert. Pin Header, 4-Pin, 0.1" Spacing, Generic                                           | ANY         |

| 8     | 2   | J3, J4                                                                             | HDR-3                              | HDR-3            | Vert. Pin Header, 3-Pin, 0.1" Spacing, Generic                                           | ANY         |

| 9     | 1   | J5                                                                                 | HDR-4POL                           | HDR-4POL         | Header, 4-pin, Polarized, AMP 3-641213-4                                                 | AMP         |

| 13    | 14  | TP1, TP2, TP3, TP4,<br>TP5, TP6, TP7, TP8,<br>TP9, TP10, TP11,<br>TP12, TP13, TP14 | TEST POINT                         | TEST POINT       | Test Point, Thru-Hole, White,<br>Mouser 534-5002                                         | KEYSTONE    |

| TABLE 6. | ISL9112 EVALUATION BOARD BILL OF MATERIALS |

|----------|--------------------------------------------|

|----------|--------------------------------------------|

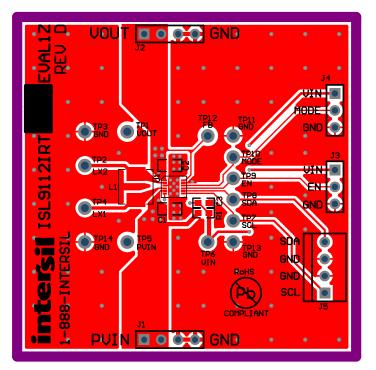

### **Evaluation Board Layout**

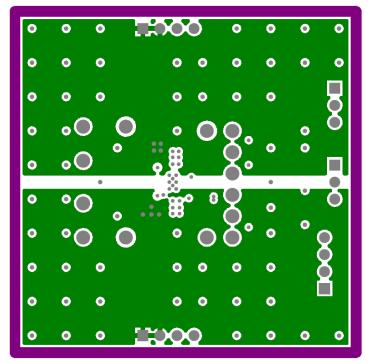

FIGURE 5. ISL9112 EVALUATION BOARD SILKSCREEN TOP

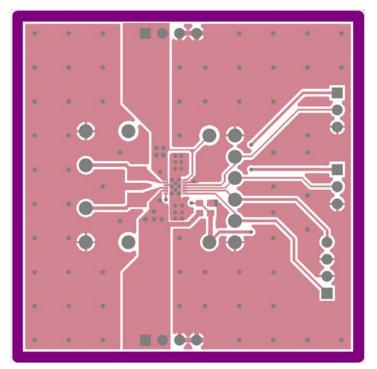

FIGURE 6. ISL9112 EVALUATION BOARD TOP COPPER

## Evaluation Board Layout (Continued)

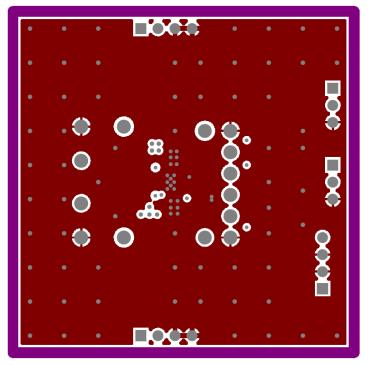

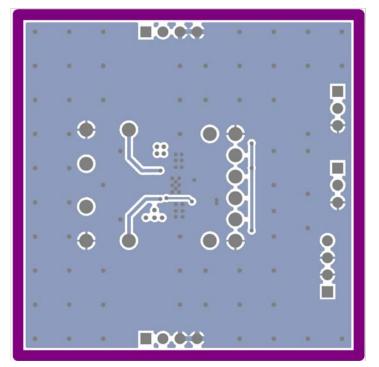

FIGURE 7. ISL9112 EVALUATION BOARD MID LAYER 1 (GND)

FIGURE 8. ISL9112 EVALUATION BOARD MID LAYER 2 (VIN AND VOUT)

### Evaluation Board Layout (Continued)

FIGURE 9. ISL9112 EVALUATION BOARD BOTTOM LAYER (GND)

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com